About

Advanced Protocol Analysis Partner

-

0 +Years in Validation

-

0 Global Standards Bodies

-

0 +Protocols Supported

-

0 +Global Deployments

Our clients are the GLOBAL Elites

In the Spotlight

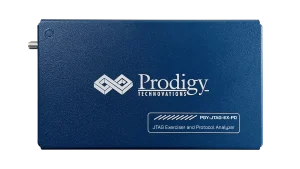

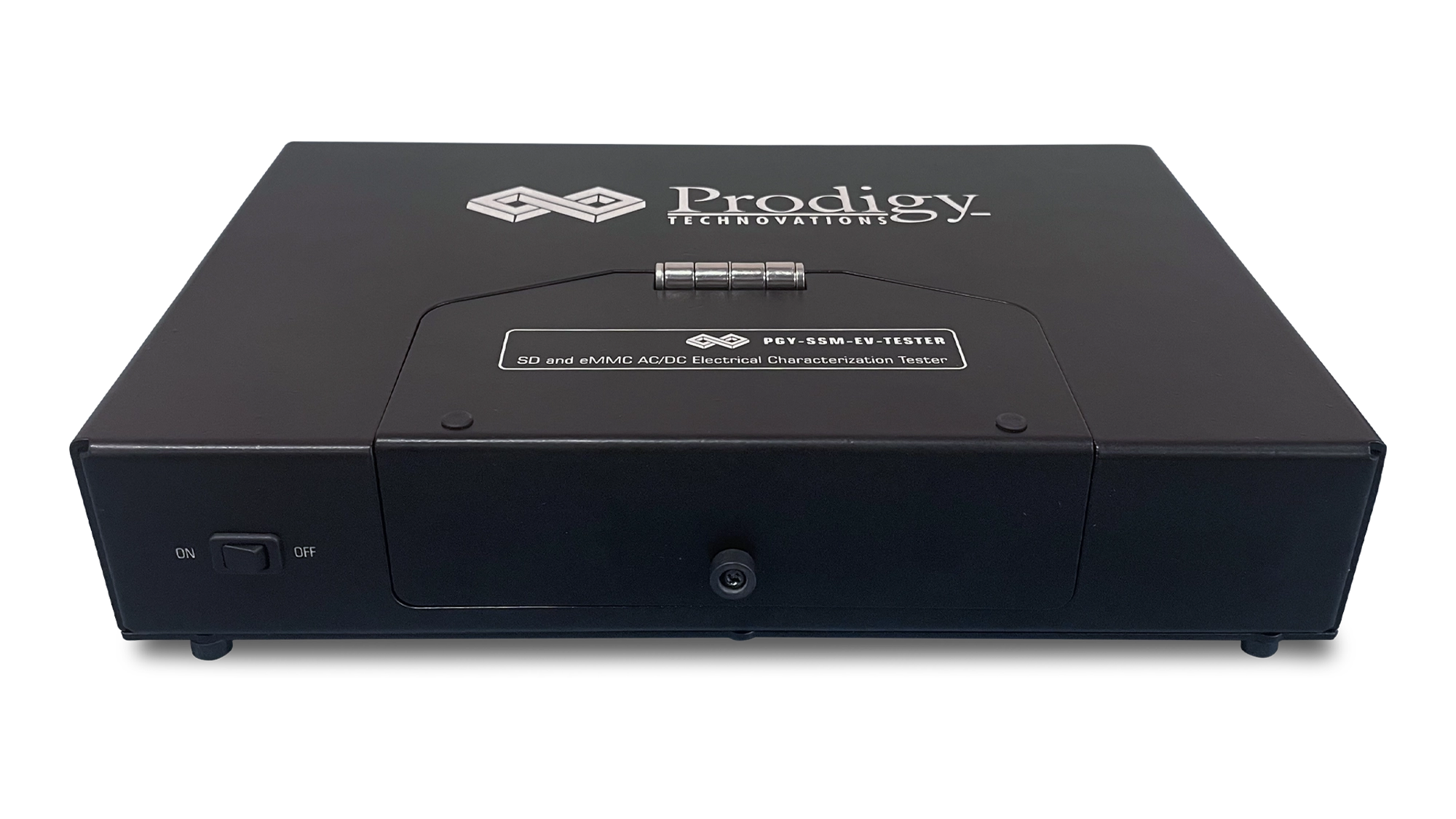

Explore Featured Products

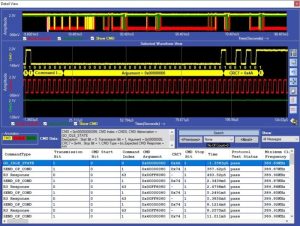

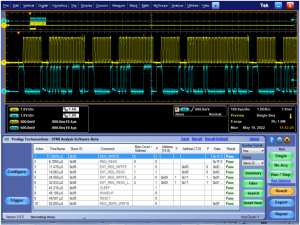

Introducing our latest generation of protocol analysis tools, engineered for the

sub-nanosecond precision required by the world's most advanced SoC designs.

Global Impact

Worldwide Expertise

We ship across the globe through our distributors. Our global distribution network spans key technology regions, ensuring that wherever your R&D center is located, a Prodigy protocol specialist is within reach.

Industry Solutions

What Prodigy Validates

From initial silicon architecture to final product sign-off, we provide the precision required to ensure every packet is captured, decoded, and validated against the world's most rigorous standards.

Automotive & Industrial

Safety-critical testing for modern software-defined vehicle architectures.

Computers & Storage

High-speed validation for next-gen data storage and consumer tech.

Embedded & Debug

Foundational toolkit for every silicon architect and hardware designer.

Mobile

Advanced validation for intricate mobile SoC interconnect layers.

Networking & Data Communication

Precision testing for high-bandwidth connectivity and data flow.

Research & Development

Defining Innovation

At Prodigy, we don't just test the future; we help architect it. With a core built on patented research and a relentless pursuit of sub-nanosecond precision, we are the silent engine behind the world's most advanced semiconductor breakthroughs.

Global Patents

With three strategic patents in protocol analysis and hardware-based decoding, our IP ensures your designs are validated with a level of accuracy that off-the-shelf solutions simply cannot reach.

- FPGA-based System for Decoding PAM-3 Signals

- Highly Scalable Architecture for PCIe Gen6 Protocol Analysis

- Passive TAP Solution

Shaping Global Protocols

We don’t just follow the rules; we help write them. As contributing members of MIPI, JEDEC, PCI-SIG, and the SD Association, we transform emerging industry standards into first-to-market validation tools.

Knowledge Hub

The Insights Lab

Access the deep-tech insights, technical architectures, and real-world implementation guides trusted by the world's leading SoC architects.

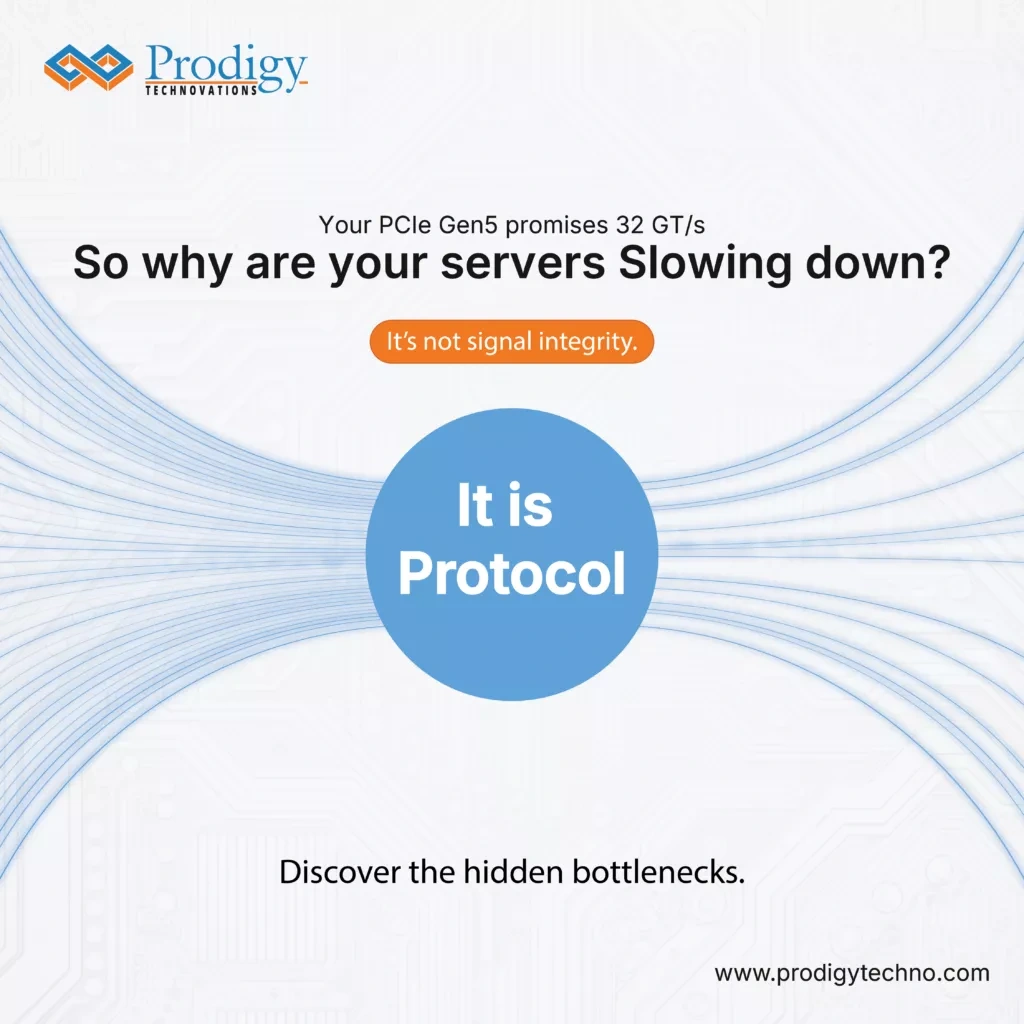

Why Gen 5 Speed is a Myth (Unless You fix the Protocol)

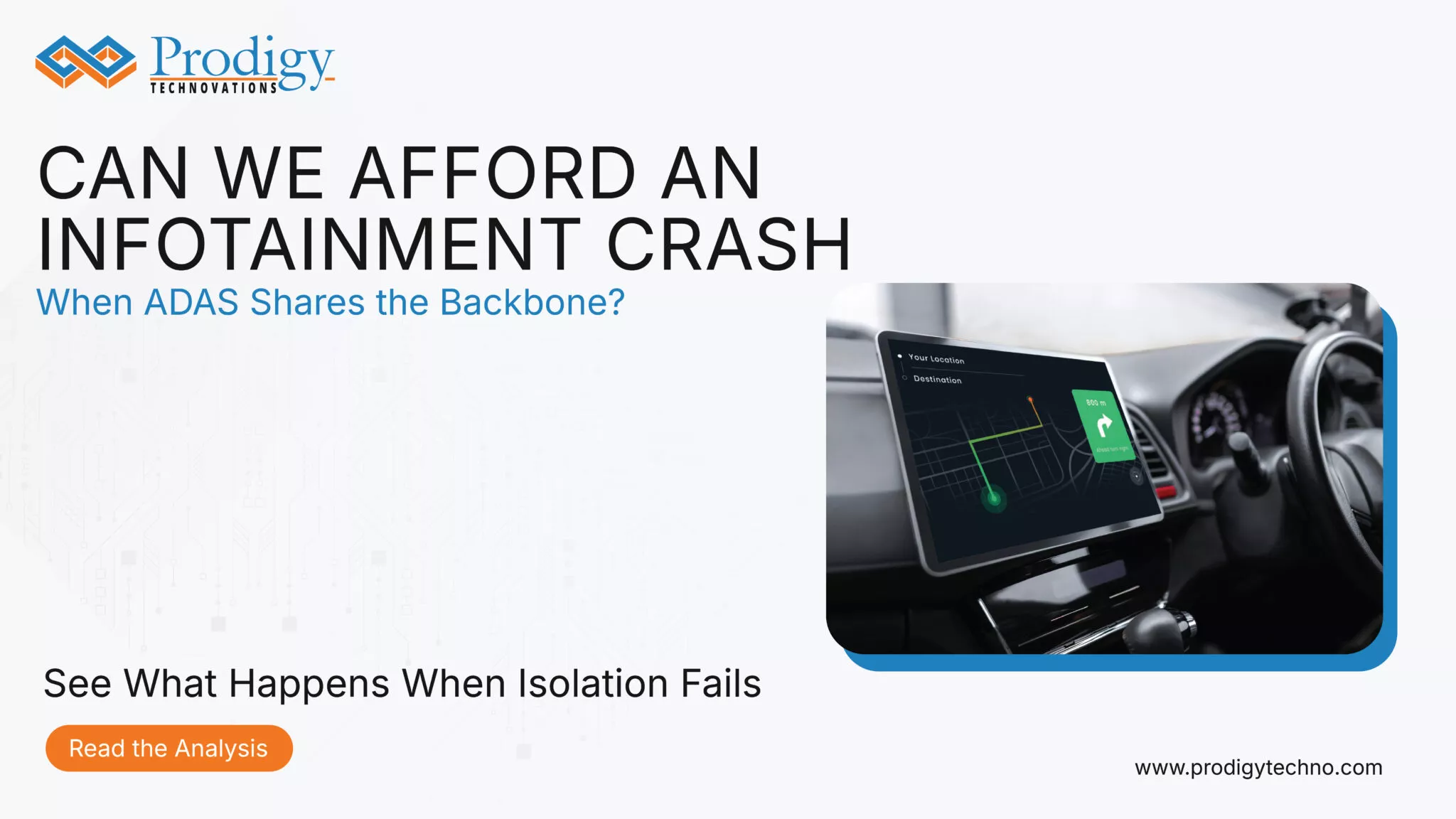

Is it possible to survive a safety-critical bus infotainment collision?

Why is SLC Cache Flushing a High-Stakes Engineering Trade-Off?

Understanding xSPI: The Future of High-Speed Flash Memory Interfaces

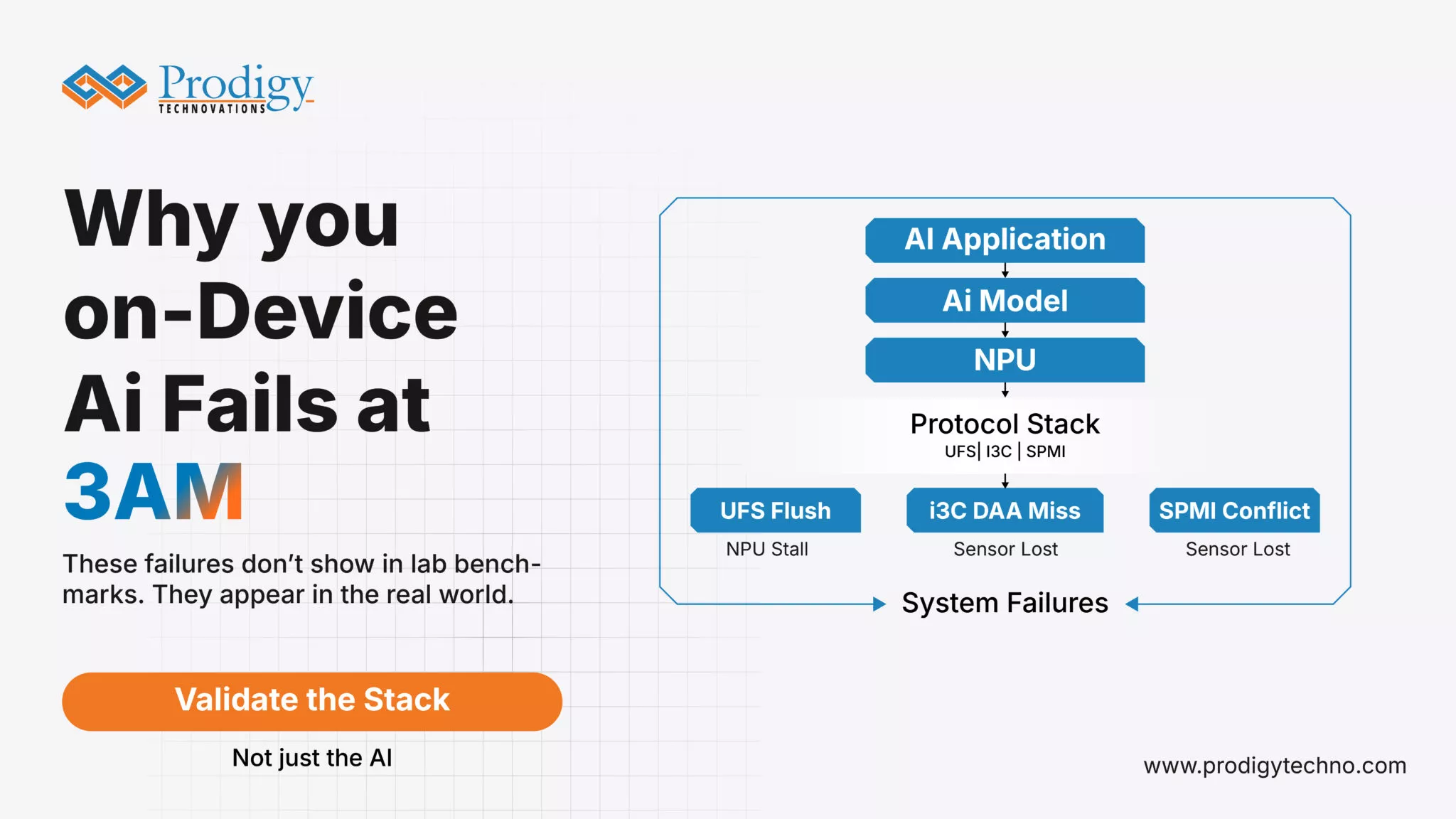

Why Your On-Device AI Feature Fails at 3am When Nobody Is Looking

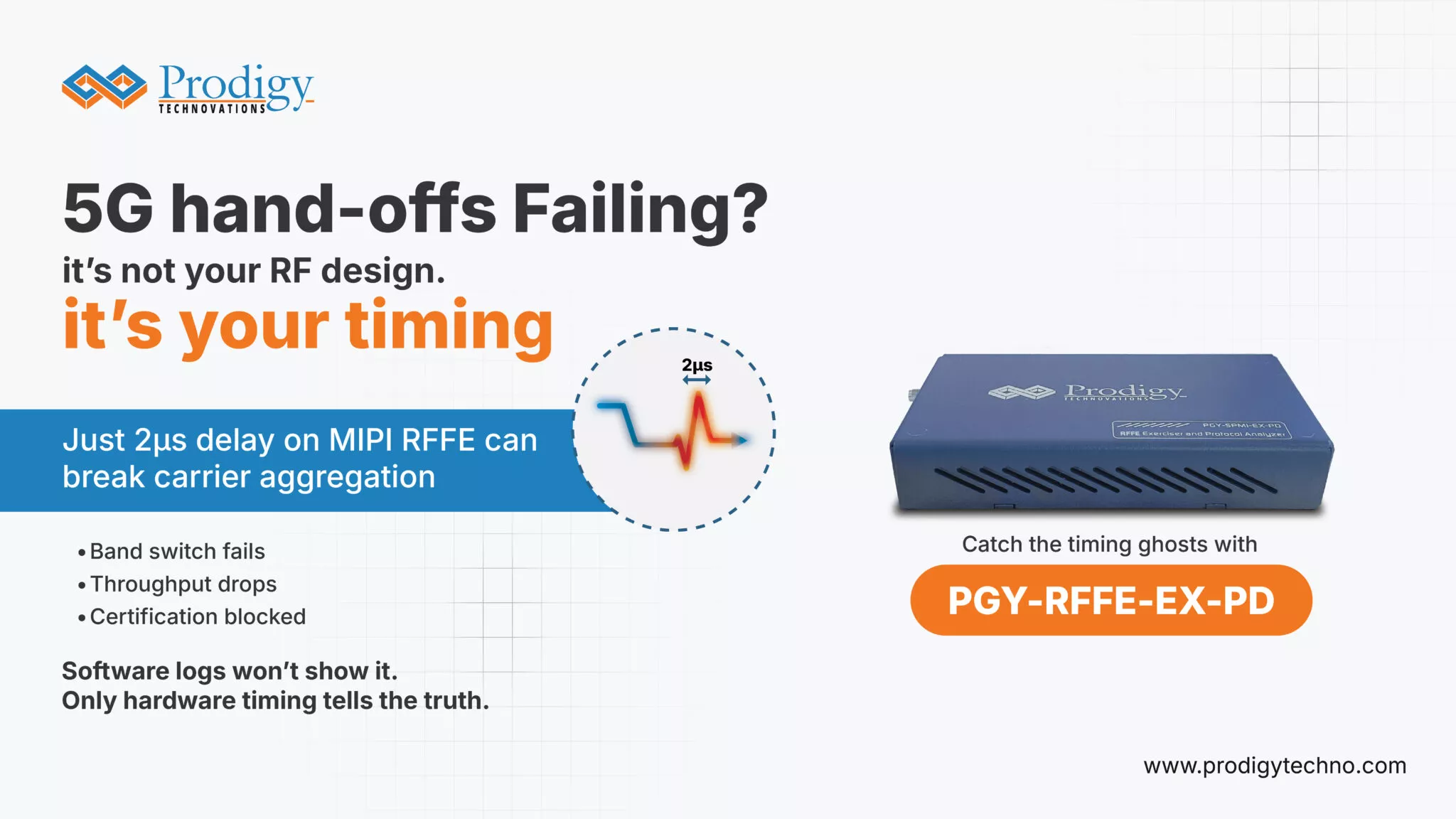

5G Hand offs: RFFE Timing is Killing Your Carrier Certification

Why Gen 5 Speed is a Myth (Unless You fix the Protocol)

Is it possible to survive a safety-critical bus infotainment collision?

Why Gen 5 Speed is a Myth (Unless You fix the Protocol)

Is it possible to survive a safety-critical bus infotainment collision?

Why is SLC Cache Flushing a High-Stakes Engineering Trade-Off?

Understanding xSPI: The Future of High-Speed Flash Memory Interfaces

Why Gen 5 Speed is a Myth (Unless You fix the Protocol)

Is it possible to survive a safety-critical bus infotainment collision?

Why is SLC Cache Flushing a High-Stakes Engineering Trade-Off?

Understanding xSPI: The Future of High-Speed Flash Memory Interfaces

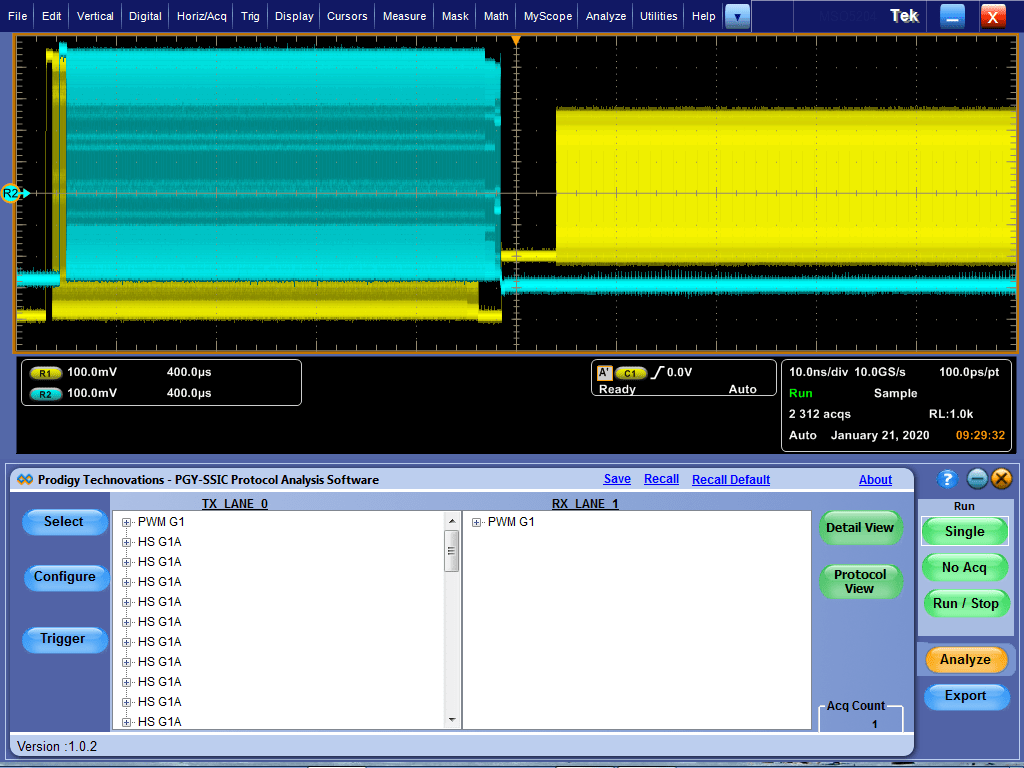

SSIC Protocol Decode Software

SD, eMMC AC/DC Tester Datasheet

SD, SDIO, eMMC Protocol Analyzer Datasheet

UFS 3.0 Protocol Analyzer Datasheet

Why Gen 5 Speed is a Myth (Unless You fix the Protocol)

Is it possible to survive a safety-critical bus infotainment collision?

Why is SLC Cache Flushing a High-Stakes Engineering Trade-Off?

Understanding xSPI: The Future of High-Speed Flash Memory Interfaces

Why Gen 5 Speed is a Myth (Unless You fix the Protocol)

Is it possible to survive a safety-critical bus infotainment collision?

Why is SLC Cache Flushing a High-Stakes Engineering Trade-Off?

Understanding xSPI: The Future of High-Speed Flash Memory Interfaces

Core Queries

Frequently Asked Questions

Core Queries